UDC 543.3, 53-032.2(045)

# A HIGH SPEED TRANSMITTER DYNAMIC EQUALIZATION METHOD FOR SERIAL LINKS

# A.A. Martirosyan

"Synopsys Armenia" CJSC

A method for signal equalization of high speed serial links transmitter is presented in this paper. To avoid signal losses and ISI effects besides receiver input signal equalization, transmitter output signal pre-equalization is also needed right before transmission. One of the known methods is pre/post emphases with constant gains, which provides pre-equalization independent of frequency. The disadvantage of this method is frequency independency which means that the signal will propagate through the channel with pre-equalized high frequency regions but independent on the data rate. To validate the proposed architecture, experiments are conducted for example, with various injected faults, for which the conventional approach of examining the eye opening at the output of the equalizer results. When data signals in the inputs of receiver come with high frequencies without equalizer and with many low and high frequency harmonics, the output system can lose the data, because high frequencies of the data can be rejected by the channel. One of the main reasons of signal rejection by the channel is the low pass filter and it can filter high frequency data signals. That's why in high speed serial links some data transferring and receiving process support blocks are used which provide signal reliable reading and help to avoid data errors and loss.

The proposed transmitter equalization mechanism can be used in the high speed input/output standards such as Universal Serial Bus (USB) which provides pre-equalization depending on a data rate.

*Keywords:* equalizer, receiver (RX), transmitter (TX), pre-emphases (P-MPH), analog front end (AFE), continuous time linear equalizer (CTLE).

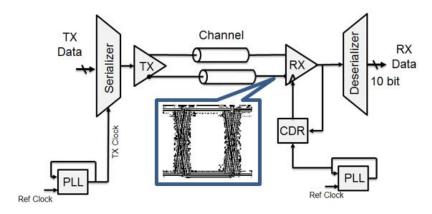

**Introduction.** In high rate data transfer systems (Fig. 1) and interfaces [1,2], where the frequency of the signal going to GHz region and signal uncertainty becomes bigger and bigger, the receiver part mission of the link becomes very challenging. Many types of signal equalization methods came up to solve the problem with signal rejection from low bandwidth channel. Especially it appears in serial links, where signal transmitting with one serial channel and, as it is known, after parallel data serialization, frequency or data rate goes up. This mainly makes the data transmission process harder.

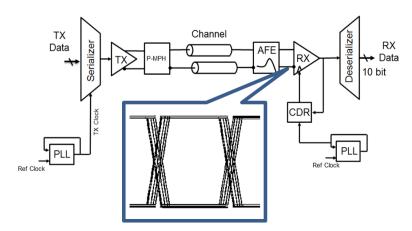

So, there are several equalization methods which could be applied either in transmitter part after the signal transmission or in the receiver analog front end (AFE)

(Fig. 2) stage right before the signal arrival. Transmitter equalization is calling preemphases and is boosting high frequency regions right before the signal transmission. This compensates high frequency signal rejection by channel and equalizes the signal at the input of the receiver side (far end).

Fig.1. Serial link

Fig.2. High Speed Serial link with P-MPH and AFE equalizer structure

Signal pre-emphases function is very important in high speed systems, where at the far end of the link signal, the eye opening could not be enough to read the true data with just receiver input equalization [3]. So, high speed parts should be pre-equalized at the right output of the transmitter to avoid the signal rejection impact on the signal eye opening at the link far end part.

As a solution, there are several methods which could implement this preemphases part and somehow compensate the channel rejection effect. But all the known methods are supporting just static high speed part pre-emphases implementation which could not be enough in case of high frequency bands.

As a conclusion, there should be a new approach which will provide preemphases equalization in the output of the transmitter, and the boosting of high speed parts will dynamically depend on the frequency range of the data signal. This system will improve the data signal eye vertical and horizontal openings and will help to avoid wrong signal detection at the far end of the channel. This will decrease the bit error rate (BER) of the receiver input stage and will provide high reliability of data detection. Of course, it will make serial link performance better and will relax the requirements of the RX input equalizer.

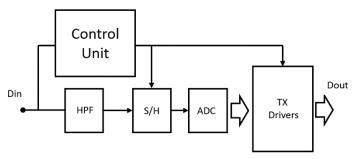

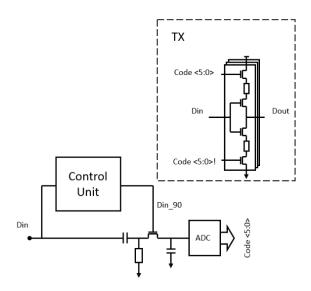

1. Transmitter Dynamic Equalization Circuit Architecture. The structure of the proposed transmitter dynamic equalization for high speed serial AC links is presented in Fig.3.

Fig.3. The proposed transmitter dynamic equalization circuit structure

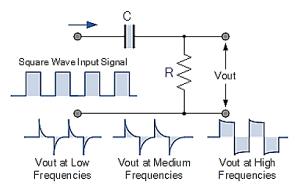

In this architecture, input serial data signal come to the control unit block which controls the sample-hold part switch. Beside that, Din signal is appled to the high pass filter (HPF) and its output sampling by sample/hold block (S/H). Each sampled voltage includes information about input frequency (Fig. 4).

Fig.4. High pass filter response of signal different frequency

$$f_c = \frac{1}{2\pi RC}.$$

After sampling, ADC converts the sampled voltage to digital code. This code controls the transmitter output driver's active part numbers. Pre-emphases boosting coefficient depends on the active numbers of the TX driver matrix. As a result, the system (Fig. 5) detects the input signal frequency and dynamically controls the enabled amount of output drivers and changes the pre-emphasis portion of signal swing, so because of that, the signal is transmited through the channel. This technique is called transmitter dynamic equalization method which provides good channel equalization at the near end of the link and pre-equalizing signal for far end.

Fig.5. The proposed transmitter control method

In high speed serial AC links, combinational solutions of receiver and transmitter equalization should be applied to make RX input eye opening detectable.

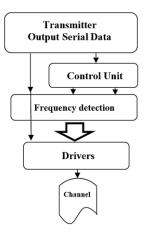

2. Operation Principle and Equalization. The proposed method block diagram is presented in Fig.6. It shows the transmitter data path from the serializing stage to the channel. At first, the transmitter output serial data is appled to the control unit which controlls the frequency detection sampling part. The transmitter output serial data also goes to the final drivers' stage. The frequency detection part at first apples data signal to the high pass filter to make intermediate signal with different slops. After that sample/hold stage samples this intermediate signal with correct data signal phase. Sampled voltage will be proportional to the initial data rate. It will give information about data

frequency for making a true decision about how much final data should be preemphased right after final transmission [4].

The proposed method will dynamically change the boost of high speed segments of data signal and will well equalize the data signal propagation at the far end of the link. Before data reading, it should be equalized with different gain in a large frequency spectrum and for this range, the channel and equalizer overall frequency response should be settled. If it is not close to constant, it should be calibrated from the equalizer part of overall system frequency response.

All these processes should be done to improve the receiver input signal eye horizontal and vertical openings, and also reduce as much as possible the received signal BER.

Fig.6. The block diagram of the equalization method

As it was mentioned above, the data signal coming from the channel and equalizer is needed for compensating the channel low pass frequency response through lines that can bring data errors over PVT and poor signal eye opening.

The equalization process starts from the far end of the channel (Fig.7). Control has a 3-bit output digital signal which is controlled by equalized RX equalizer output and is changing for overall frequency response calibration. After several iterations, when the loop is already locked, control generates an output final code to provide optimal overall frequency response for further processing of the signal.

**3. Simulation Results.** Simulations have been performed, using circuit level simulator Hspice [5] for 20 PVT corners, including SS (slow-slow), TT (typical-typical), FF (fast-fast), SF (slow-fast), FS (fast-slow) with supply voltage and temperature variations to estimate the bit error rate (BER), and the channel far end RX input eye vertical and horizontal openings.

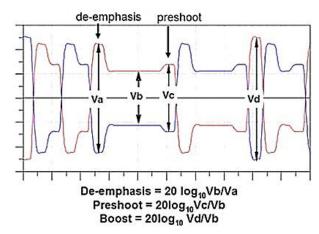

Fig. 7 shows the transmitter output equalization definitions.

The table shows the simulation results accordingly for FF (-40°) and SS (125°) main PVT corners for BER and the eye horizontal and vertical openings for the 10Gbit/s data rate.

Table

Simulation results of the three main corners 10 Chit/s

| Corner   | Horizontal opening | Vertical opening | BER |

|----------|--------------------|------------------|-----|

| Unit     | ps                 | mV               | #   |

| TT (55)  | 85                 | 120              | 5   |

| FF (-40) | 87                 | 150              | 7   |

| SS (125) | 73                 | 95               | 12  |

Fig.7. TX dynamic equalization plots

**Conclusions.** A high speed transmitter dynamic equalization method has been designed to compensate the frequency response of the channel. A high-speed equalizer will open the far end eye, and will reduce the received data BER up to 40% in respect to static equalization.

The method can be implemented for input/output protocols such as USB, PCI and other modern special I/O interfaces.

## References

- Baker R.J. CMOS Circuit Design, Layout and Simulation. Second Edition. 2008. P. 1045.

- 2. **Chada A.R.** Mutnury B. Simulation Challenges in Designing High Speed Serial Links // IEEE 62nd Electronic Components and Technology Conference (ECTC). -2012.

- 3. **Liu J. and Lin X.** Equalization in high-speed communication systems // IEEE Circuits and Systems Magazine. -2004. -P. 4-17.

- 4. A 10Gb/s receiver w/ equalizer and on-chip monitor in 0.11um CMOS / Y. Tomita, M. Kibune, J. Ogawa, et al // Journal of Solid-State Circuits. April, 2005.- Vol. 40, No. 4.

- 5. Hspice Application Manual, Synopsys Inc. 2010. -P.196.

Received on 15.03.2018. Accepted for publication on 05.06.2018.

# ՏՎՅԱԼՆԵՐԻ ՀԱՋՈՐԴԱԿԱՆ ՀՈՍՔՈՒՂԻՈՎ ԱՐԱԳԱԳՈՐԾ ՀԱՂՈՐԴՉԻ ԴԻՆԱՄԻԿԱԿԱՆ ՀԱՄԱՀԱՐԹԵՑՄԱՆ ՄԵԹՈԴ

#### Ա.Ա. Մարտիրոսյան

Ներկալազված է հաջորդաբար տվյալներ փոխանգող արագագործ՝ հաղորդչի ազդանշանի համահարթեցման մեթոդր։ Ազդանշանային կորուստներից և միջազդանշանային խանգարումներից խուսափելու նպատակով ընդունիչի մուտքում, ազդանշանի համահարթեզումից բացի, անհրաժեշտ է կատարել ազդանշանի նախնական համահարթեցում անմիջապես հաղորդչի ելքում։ Հայտնի մեթոդներից մեկր ազդանշանի նախնական / հետագա ընդգծումն է հաստատուն ուժեղազմամբ, որն ապահովում է ազդանշանի նախնական hամահարթեցումը՝ անկախ hաճախությունից։ Մեթոդի թերությունն անկախությունն է հաճախությունից․ դա նշանակում է՝ նախապես համահարթեցվում են հոսքուղով տարածվող ազդանշանի միայն բարձր հաճախականային տեղամասերը՝ անկախ տվյալների արագությունից։ Առաջարկվող ճարտարապետությունը վավերացնելու համար հավաքվել են փորձնական օրինակներ՝ տարբեր սխալանքներով, տարբեր մոտեցումների օրինակներ և համահարթեցուցչի ելքում կատարվել են աչքաչափ բացվածքի չափումներ։ Երբ ընդունիչի մուտք է գալիս բարձր հաճախականալին, չհամահարթեցված և բարձր, և զածրիաճախականալին հարմոնիկներ պարունակող ազդանշան, ապա հնարավոր է տվյայների կորուստ, քանի որ հոսքուղին կարող է ճնշել բարձրհաճախականային տիրույթները։ Տվյալների բարձրհաճախականային տիրույթները ճնշվում են կանայի միջոցով, քանի որ այն ներկայացնում է բարձրհաճախականային ֆիլտր։ Այդ իսկ պատճառով հաջորդաբար տվյալներ փոխանցող արագագործ համակարգերում տվյալների հաղորդման և ընդունման ընթազքում աշխատում են գործընթացին աջակցող բլոկներ, որոնք ապահովում են հուսալի րնթեռնելի տվյայներ և նպաստում են՝ խուսափելու սխալանքներից, ինչպես նաև տվյալների կորստից։

Հաղորդչի համահարթեցման առաջարկվող մեխանիզմը կարող է օգտագործվել արագագործ մուտք/ելք այնպիսի ստանդարտում, ինչպիսին է հանրանշանակ հաջորդական դողը (USB), որն ապահովում է նախնական համահարթեցում՝ կախված տվյալների արագությունից։

**Առանցքային բառեր.** համահարթեցում, ընդունիչ, հաղորդիչ, նախնական ընդգծում, անալոգային ինտերֆելս, շարունակական ժամանակային գծային համահարթեցում։

# МЕТОД ДИНАМИЧЕСКОГО ВЫРАВНИВАНИЯ ВЫСОКОСКОРОСТНОГО ПЕРЕДАТЧИКА С ПОСЛЕДОВАТЕЛЬНЫМ КАНАЛОМ ДАННЫХ

## А.А. Мартиросян

эквализации сигналов преобразователя Представлен метод скоростных последовательных связей. Во избежание потерь сигнала и межсигнальных помех, кроме эквализации входного сигнала приемника, необходимо провести предварительную эквализацию выходного сигнала передатчика непосредственно перед передачей. Одним из известных методов является предварительное/дальнейшее акцентирование сигнала с постоянным коэффициентом усиления, который обеспечивает предварительную эквализацию независимо от частоты. Недостатком метода является независимость от частоты. Это означает, что сигнал будет распространяться по каналу с предварительно эквализированными высокочастотными областями, но не зависящими от скорости передачи данных. Для тестирования предлагаемой архитектуры были собраны экспериментальные примеры с различными ошибками, примеры различных подходов и измерений открытия глаза на выходе эквалайзера. В случае, когда сигналы данных на входах приемника поступают с высокими частотами без эквалайзера и со многими гармониками низких и высоких частот, выходная система может потерять данные, поскольку высокие частоты даты могут отклоняться по каналу. Одной из основных причин отказа сигналов по каналу через PVT является высокочастотный фильтр, фильтровать высокочастотный сигнал данных. вышесказанного, в высокоскоростных последовательных каналах используются некоторые блоки передачи данных и приема, обеспечивающие надежное считывание сигнала во избежание ошибок и потерь данных.

Предлагаемый механизм эквализации передатчика может использоваться в высокоскоростных стандартах ввода/вывода, таких как универсальная последовательная шина (USB), которая обеспечивает предварительную эквализацию, в зависимости от скорости передачи данных.

*Ключевые слова*: эквализация, приемник, передатчик, предварительно напряженный, аналоговый интерфейс, непрерывное линейное выравнивание.