УДК 621.382

# СРАВНИТЕЛЬНАЯ ОЦЕНКА РАССЕИВАЕМОЙ МОЩНОСТИ НАКОПИТЕЛЕЙ КМОП СТАТИЧЕСКИХ ОПЕРАТИВНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ

# О.А. Петросян<sup>1</sup>, Н.Б. Авдалян<sup>2</sup>, Г.Ш. Меликян<sup>1</sup>

<sup>1</sup> Государственный инженерный университет Армении (Политехник) <sup>2</sup> 3AO "Синопсис Армения"

При разработке сверхбольших интегральных схем комплементарных металлокисел-полупроводник (КМОП) запоминающих устройств оценка рассеиваемой мощности является неотъемлемой частью их проектирования. Проведен сравнительный анализ рассеиваемой мощности накопителей на основе различных схемотехнических решений построения запоминающих ячеек при использовании библиотеки с технологическими нормами SAED EDK в 28 нм.

*Ключевые слова:* запоминающая ячейка, накопитель, рассеиваемая мощность, моделирование.

Введение. При проектировании сверхбольших интегральных схем (СБИС) запоминающих устройств (ЗУ) важное значение имеет оценка рассеиваемой мощности (особенно статической) элементной базы запоминающих ячеек (ЗЯ) и накопителей на их основе, особенно на ранних стадиях проектирования. При этом актуальной задачей является сравнительный анализ рассеиваемой мощности накопителей на основе различных схемотехнических решений построения ЗЯ при использовании библиотеки с технологическими нормами SAED EDK в 28 нм.

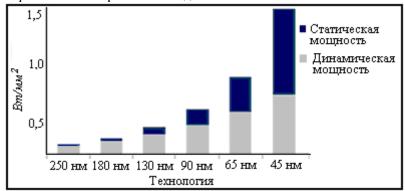

Рассеиваемая мощность состоит из двух составляющих: статической  $P_{cm}$  и динамической  $P_{\partial un}$  (рис. 1) [1]. Динамическая мощность рассеивается в активном режиме, т.е. при переключениях логических элементов (ЛЭ). Статическая мощность не зависит от активности внутренней логики и рассеивается в пассивном режиме или в режиме ожидания.

Рис. 1. Уровень потребления мощности при масштабировании технологии

Из рис. 1 видно, что при масштабировании технологии статическая составляющая мощности становится соизмеримой с динамической мощностью.

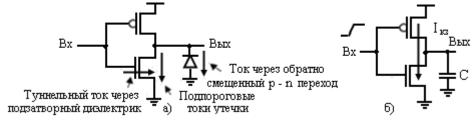

**Статическая рассеиваемая мощность.** Эта мощность обусловлена токами утечки: током обратно смещенного p - n перехода, подпороговым током и туннельным током через подзатворный диэлектрик (рис. 2,3) [2,3]. Каждый механизм является доминирующим в разных областях структуры (рис. 3) [3].

Рис. 2. Направления токов утечки для статической (а) и динамической (б) мощностей

Статическая мощность не является функцией тактовой частоты, в то время как рассеиваемая мощность, наоборот, представляет линейную функцию от тактовой частоты:

$$P_{pac}(F_{my}) = A F_{my} + P_{cm} , \qquad (1)$$

где А - коэффициент, не зависящий от тактовой частоты.

Рис.3. Тенденции развития динамической и статической рассеиваемых мощностей

Ток утечки обратно смещенного p - n перехода. Этот ток возникает тогда, когда на вход ЛЭ приложен низкий логический уровень напряжения и выход ЛЭ - сток n МОП транзистора подключается к шине питания (рис. 2). В результате между стоком и подложкой возникает обратно смещенный p - n переход, через который течет ток утечки [1]:

$$J = A \frac{EV_{pn}}{E_g^{1/2}} exp \left(-B \frac{E_g^{1/2}}{E}\right),$$

где  $A=\sqrt{2m^*q^3}/4\pi^3h^2$ ,  $B=4\sqrt{2m^*}/3hq$ ;  $m^*$  - эффективная масса электрона;  $E_g$  - ширина запрещенной зоны;  $V_{pn}$  - напряжение обратно смещенного p-n перехода; E - напряженность электрического поля; q - заряд электрона; h - постоянная Планка.

Ток подпороговой утечки. Этот ток возникает тогда, когда n МОП транзистор закрыт, разница напряжений между его стоком и истоком равна напряжению питания и через канал протекает ток [1,3]:

$$I_{sub} = \mu \cdot C_{ox} \cdot \varphi_T^2 \cdot e^{l,8} \cdot \frac{W}{L} \cdot e^{\frac{V_{GS} - V_{th}}{n\varphi_T}} \left(1 - e^{\frac{V_{DS}}{\varphi_T}}\right), \tag{2}$$

где  $\mu$  - подвижность носителей заряда;  $C_{OX}$  - емкость подзатворного окисла;  $\varphi_T$  - термический потенциал; W, L - ширина и длина канала транзистора;  $V_{GS}$  - напряжение затвор-исток;  $V_{th}$  - пороговое напряжение транзистора; n - технологически зависимый параметр;  $V_{DS}$  - напряжение сток-исток.

Туннельный ток через подзатворный диэлектрик. Этот ток возникает тогда, когда носители заряда проходят через подзатворный диэлектрик вследствие туннельного эффекта, и определяется следующим выражением [1,3]

$$I_{ox} = W \cdot L \cdot A \cdot \left(\frac{V_{ox}}{t_{ox}}\right)^{2} exp\left(\frac{-B\left(I - \left(I - V_{ox}/\varphi_{ox}\right)^{3/2}\right)}{V_{ox}/\varphi_{ox}}\right),$$

где  $A=q^3/16\pi^2h\phi_{ox}$ ;  $B=4\pi\sqrt{2m_{ox}}\phi_{ox}^{3/2}/3hq$ ;  $m_{ox}$  - эффективная масса туннелированных частиц;  $\phi_{ox}$  - высота туннельного барьера;  $\mathbf{t}_{ox}$  - толщина окисла.

**Динамическая рассеиваемая мощность.** Эта мощность состоит из двух основных компонентов: ЛЭ, необходимого для перезарядки выходных емкостей, и внутренней мощности, которая включает в себя:

- потребление, обусловленное током короткого замыкания, который протекает через ЛЭ, когда при его переключении открыты оба р-МОП и n-МОП транзистора (рис. 2);

- мощность, необходимую для перезарядки внутренних емкостей ЛЭ. Динамическая потребляемая мощность определяется выражением

$$P_{duu} = \left(C_{sd}V_{dd}^{2}F_{mu}\right) + \left(t_{gn/13}V_{dd}I_{gmn}F_{mu}\right),\tag{3}$$

где  $C_{9\phi}$  - эффективная емкость устройства;  $V_{dd}$  - напряжение питания;  $F_{m^q}$  - тактовая частота;  $t_{6n/19}$  - время переключения ЛЭ;  $I_{6mn}$  - эффективная величина внутреннего тока переключения (сумма тока короткого замыкания и тока, необходимого для перезарядки внутренних емкостей).

Первое слагаемое в (3) выражает мощность переключения, второе - внутреннюю мощность. Из (3) следует, что  $P_{\partial u h}$  пропорциональна  $F_{m u}$ .

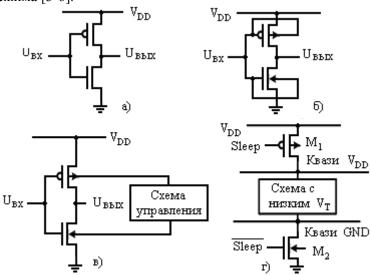

Схемотехнические решения снижения статической рассеиваемой мощности. Снижение статической рассеиваемой мощности на схемотехническом уровне заключается в управлении пороговым напряжением МОП транзисторов, типовой КМОП структуры (рис. 4a) в зависимости от рабочего режима [3-6].

Рис. 4. Схемотехнические решения снижения статической мощности: а - типовой инвертор, б - инвертор с дополнительными электродами, в - инвертор со схемой управления, г - инвертор с квазишинами питания

В ЛЭ (рис. 46) подложки р-МОП и n-МОП транзисторов подключены к затворам. В случае, когда на входе имеется напряжение логической единицы  $(V_{dd})$ , пороговое напряжение  $(V_{nop})$  уменьшается, и, следовательно, увеличивается ток, перезаряжающий нагруженную емкость, что приводит к повышению быстродействия. В случае, когда на входе имеется напряжение логического нуля  $(0\ B),\ V_{nop}\ n$ -МОП транзистора не меняется, обеспечивая малые токи утечки. Таким образом, обеспечивается автоматическое изменение  $V_{nop}$  МОП транзисторов.

В ЛЭ (рис. 4в) подложки p-МОП и n-МОП транзисторов подключены к схеме управления, обеспечивая управление  $V_{\text{пор}}$  транзисторов смещением подложки благодаря использованию эффекта влияния подложки. В активном

режиме на подложку p-МОП транзистора подается напряжение питания  $V_{dd}$ , а на подложку n-МОП транзистора - 0 B, обеспечивая таким образом низкое  $V_{nop}$ . В пассивном режиме на подложки p- и n- канальных МОП транзисторов подаются напряжения  $2V_{dd}$  и - $V_{dd}$  соответственно, и в результате  $V_{nop}$  увеличивается. Таким образом, в пассивном режиме уменьшается статическая рассеиваемая мощность, а в активном режиме повышается быстродействие.

В ЛЭ рис. 4г используются транзисторы с разным  $V_{nop}$  - малым (транзисторы блока) и большим (транзисторы М1 и М2). Транзисторы с малым  $V_{nop}$  обеспечивают высокое быстродействие, а транзисторы с высоким  $V_{nop}$  отключают схему в те моменты времени, когда она должна находиться в пассивном режиме сигналами sleep и инверсный sleep. Sleep-режим работы существенно уменьшает статическую рассеиваемую мощность из-за больших токов утечки у транзисторов с малым значением  $V_{nop}$ . Недостатками этого ЛЭ является дополнительная емкость, привносимая транзисторами М1 и М2, что уменьшает быстродействие, а также появление дополнительных помех в цепях питания (емкость виртуальной шины "земли" намного больше реальной земли).

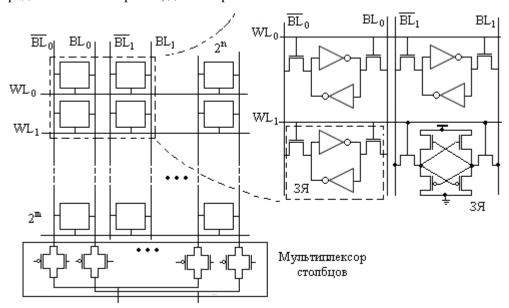

Статические оперативные ЗУ являются источником статической рассеиваемой мощности, т.к. не все ЗЯ находятся в активном режиме (рис. 5). Для хранения одного бита информации необходима одна ЗЯ, состоящая из двух инверторов и двух транзисторов - 6Т ЗЯ. Проведем сравнительный анализ применения ЛЭ, представленных на рис. 5, для построения ЗЯ.

Рис. 5. Электрическая схема накопителя ЗУ

Результаты моделирования ЛЭ, приведенных на рис. 4а,б, при использовании библиотеки с технологическими нормами SAED EDK в 28 *нм* представлены в табл.1.

Таблица 1 Значения статических и динамических токов ЛЭ

| ЛЭ (рис. 4а) |              | ЛЭ (рис. 4б) |              |  |

|--------------|--------------|--------------|--------------|--|

| статический  | динамический | статический  | динамический |  |

| ток          | ток          | ток          | ток          |  |

| 4,57 нА      | 10,597 нА    | 2,95 нА      | 14,76 нА     |  |

Из таблицы видно, что в статическом режиме ток ЛЭ, приведенного на рис. 46, меньше, чем ток ЛЭ, приведенного на рис. 4а, а динамический ток больше, чем ток ЛЭ, приведенного на рис. 4а. Таким образом, ЛЭ, приведенный на рис. 4б, нецелесообразно использовать для построения накопителя ЗУ, поскольку, как видно из электрической схемы ЗЯ (рис. 5), оба инвертора ЗЯ всегда находятся в активном режиме, что может привести к существенному повышению динамического тока ЗЯ.

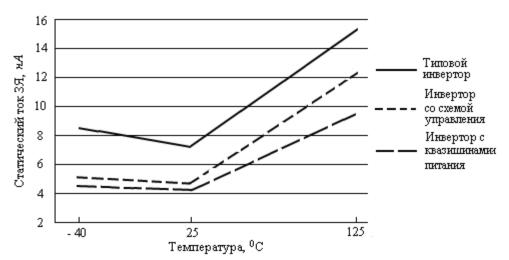

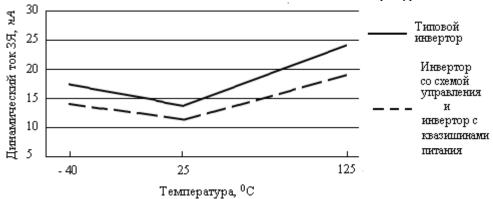

Рассмотрим возможность применения инверторов, приведенных на рис. 4в,г, для построения 3Я. В результате моделирования 3Я, построенных на основе ЛЭ (рис. 4в,г), согласно рис. 6, полученные зависимости статических и динамических токов от температуры приведены на рис. 7-8.

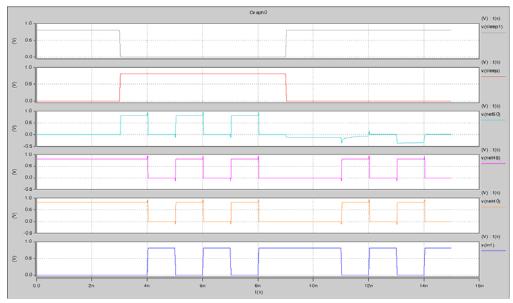

Рис. 6. Временные диаграммы для определения статических и динамических токов

Рис. 7. Зависимости статических токов ЗЯ от температуры

Рис. 8. Зависимости динамических токов ЗЯ от температуры

На основе электрической схемы накопителя статической оперативной ЗУ проведено моделирование при информационной емкости 4 и 2  $\kappa$ байм, температурах - 40, 25 и 125  $^{0}C$  и напряжении питания 0,9 B с использованием ЗЯ, построенных на основе применения инверторов, приведенных на рис. 4а, в, г. Накопители с информационной емкостью 4 и 2  $\kappa$ байм состояли из 4-х байтовых секций с 8-ю битовыми шинами. В табл. 2 приведены результаты моделирования для накопителя 4  $\kappa$ байм. Как видно из таблицы, статические и динамические токи накопителя с информационной емкостью в 2  $\kappa$ байм почти в два раза меньше аналогичных значений, полученных для 4  $\kappa$ байм.

| Темпера-             | Типовой инвертор       |                        | Инвертор с управляемым |                        | Инвертор с шинами |                        |

|----------------------|------------------------|------------------------|------------------------|------------------------|-------------------|------------------------|

| тура, <sup>0</sup> С |                        |                        | пороговым напряжением  |                        | квазипитания      |                        |

|                      | стати-                 | динами-                | стати-                 | динами-                | стати-            | динами-                |

|                      | ческий                 | ческий                 | ческий                 | ческий                 | ческий            | ческий                 |

|                      | ток, $A$               | ток, $A$               | ток, $A$               | ток, $A$               | ток, $A$          | ток, $A$               |

| - 40                 | 3,233·10 <sup>-4</sup> | 8,071·10 <sup>-4</sup> | 2,554·10 <sup>-4</sup> | 6,860·10 <sup>-4</sup> | 2,004·10-4        | 6,457·10-4             |

| 25                   | 1,681·10-4             | 4,092·10 <sup>-4</sup> | 1,412·10-4             | 3,560·10 <sup>-4</sup> | 1,093·10-4        | 3,355·10 <sup>-4</sup> |

| 125                  | 4,421·10-4             | 6,477·10-4             | 3,625·10 <sup>-4</sup> | 5,570·10-4             | 2,829·10-4        | 5,246·10-4             |

Используя приведенные в табл. 2 результаты, можно с достаточной точностью оценить статические и динамические рассеиваемые мощности для накопителей как с большой, так и с малой информационной емкостью, ЗЯ которых построены на основе инверторов, приведенных на рис. 4а, в и г.

#### Выводы

- 1. Дан анализ рассеиваемой мощности КМОП СБИС и приведены механизмы их компонентов.

- 2. В результате анализа схемотехнических решений снижения статической рассеиваемой мощности, а также их моделирования получены зависимости статических и динамических токов от температуры для технологических норм SAED EDK в 28 *нм*.

- 3. Накопители с информационной емкостью в 4 *кбайт* на основе ЗЯ с управляемым пороговым напряжением и ЗЯ с квазишинами питания обеспечивают меньшую статическую (16 и 35%) и соответственно меньшую динамическую (16 и 35%) мощности, чем ЗЯ на основе типовых инверторов.

- 4. Полученные результаты позволяют произвести выбор схемотехнического решения ЗЯ для построения накопителей ЗУ с малой рассеиваемой мощностью.

#### СПИСОК ЛИТЕРАТУРЫ

- 1. **Yuanlin Lu.** Power and performance optimization of static CMOS citcuits with variation.-Auburn, Alabama, August, 2007. 142 p.

- Leakage Current: Moore's Law Meets Static Power /Nam Sung Kim et al // Authorized licensed use limited to: Rice University. Downloaded on January 26, 2009 at 17:14 from IEEE Xplore. Restrictions apply, 2009. - P. 68-75.

- Leakage Current Mechanisms and Leakage Reduction Techniques in Deep-Submicrometer CMOS Circuits / K. Roy et al // Proceedings of IEEE.- New York, Feb. 2003. - V.91, n.2.-P. 305-327.

- 4. **Мурашко И.А.** Методы оценки рассеиваемой мощности в цифровых КМОП схемах // Доклады БГУИР. 2007.- № 1 (17). С. 100-108.

- 5. **Белоус А.И., Мурашко И.А., Сякерский В.С.** Методы минимизации энергопотребления при проектировании КМОП БИС // Технология и конструирование в электронной аппаратуре.- 2008. №2. С. 39-44.

- 6. **Кременецкая Я.А.** Физические ограничения в микро-наноэлектронике и их влияние на развитие информационных технологий // Вісник ДУІКТ. 2012. Т.10, № 4. С. 100-103.

Поступила в редакцию 20.01.2014. Принята к опубликованию 12.05.2014.

# ԿՄՕԿ ՍՏԱՏԻԿ ՕՊԵՐԱՏԻՎ ՀԻՇՈՂ ՍԱՐՔԵՐԻ ԿՈՒՏԱԿԻՉՆԵՐԻ ՑՐՄԱՆ ՀՋՈՐՈՒԹՅԱՆ ՀԱՄԵՄԱՏԱԿԱՆ ԳՆԱՀԱՏՈՒՄԸ

## Օ.Հ. Պետրոսյան, Ն.Բ. Ավդալյան, Գ.Շ. Մելիքյան

ԿՄՕԿ ստատիկ օպերատիվ հիշող սարքերի գերմեծ ինտեգրալ սխեմաները մշակելիս ցրման հզորության գնահատումը նրանց նախագծման անխզելի մասն է։ SAED EDK 28 *նմ* տեխնոլոգիական նորմերով կատարվել է կուտակիչների ցրման հզորության համեմատական գնահատում՝ հիշող տարրերի կառուցման տարբեր սխեմատեխնիկական լուծումների հիման վրա։

**Առանցքային բառեր**. հիշող տարր, կուտակիչ, ցրման հզորություն, մոդելավորում։

# A COMPARATIVE ESTIMATION OF THE DISSIPATED POWER OF THE STATIC RANDOM ACCESS MEMORY CMOS STORAGE

### O.H. Petrosyan, N.B. Avdalyan, G.Sh. Melikyan

When designing VLSI CMOS memory devices, power dissipation rating is an integral part of their design. A comparative analysis of the dissipated power drives based on various circuit solutions of designing memory cells by using the library with technological standards SAED EDK 28 *nm* is carried out.

Keywords: memory cell, array, power dissipation, modeling.